Digitaltechnik

Logikpegel

- Elektrischen Spannungen werden logische Zustände zugeordnet.

- Die eigentliche Spannung auf einer elektrischen Leitung ist in der Digitaltechnik nicht mehr vom Interesse.

| Zustand | Physikalische Größe | Pegel | Logischer Wert | Boolescher Ausdruck |

|---|---|---|---|---|

| Ein | \(5\si V\) | H (High) | \(1\) | true |

| Aus | \(0\si V\) | L (Low) | \(0\) | false |

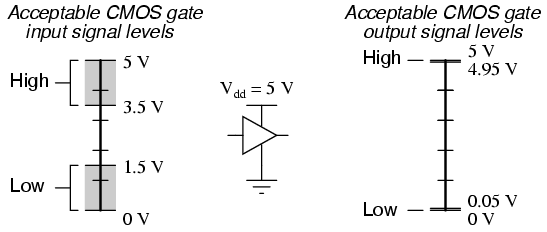

- Bei der Eingabe und Ausgabe eines Digitalsignals gibt es verschiedene Toleranzen:

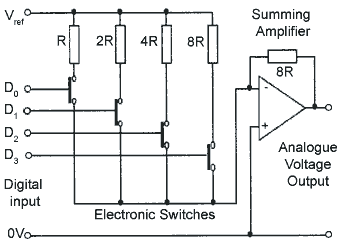

Analog-Digital-Wandler

Flash-Wandler

Aufgabe

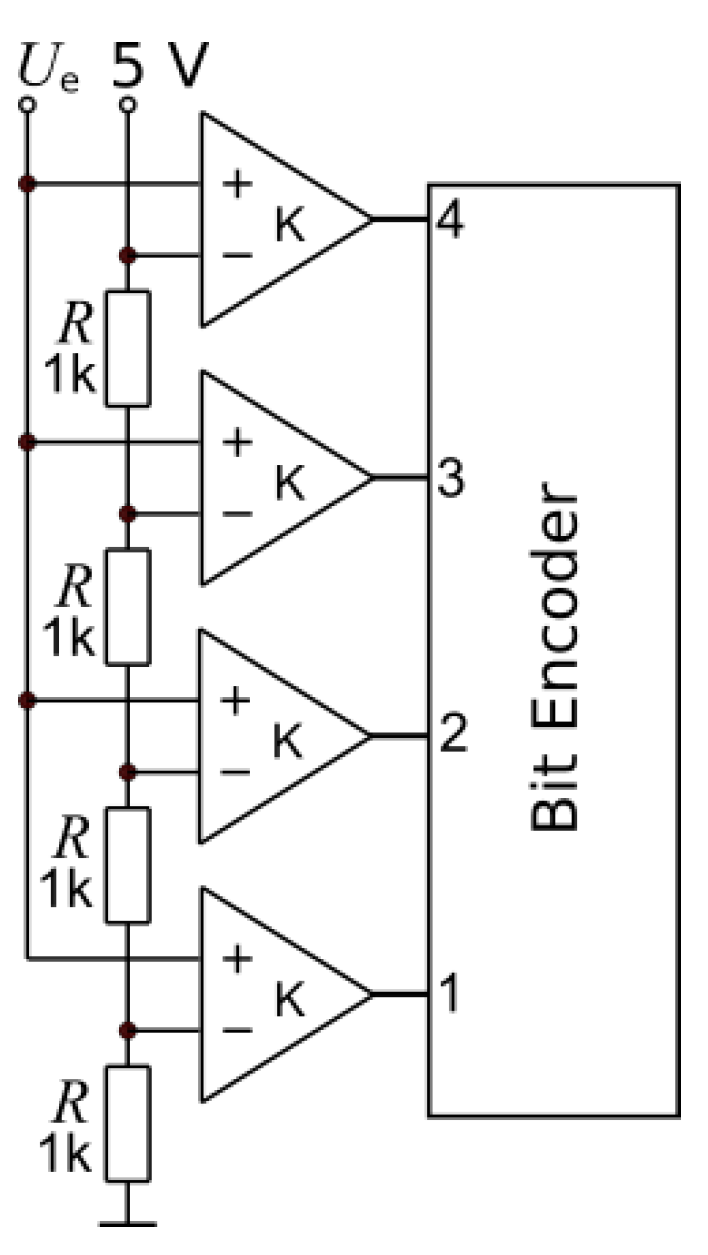

Die folgenden Abbildung zeigt das Blockschaltbild eines ADCs mit einem Messbereich von 0 bis 5 V. Welche OPV-Ausgänge werden aktiviert, wenn eine Eingangsspannung von 4,5 V angelegt wird?

Abbildung siehe oben

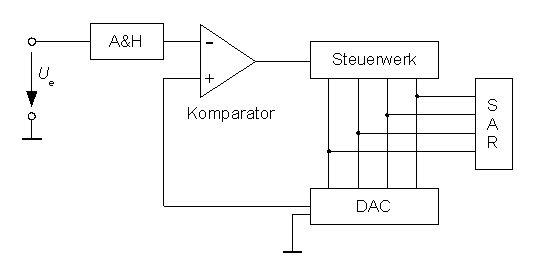

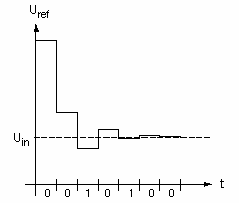

ADC mit Sukzessive-Approximation

Logikgatter

Theorie

UND / AND

ODER / OR

Negator / Inverter

Exlusiv-Oder / XOR

Elektrotechnischer Aufbau

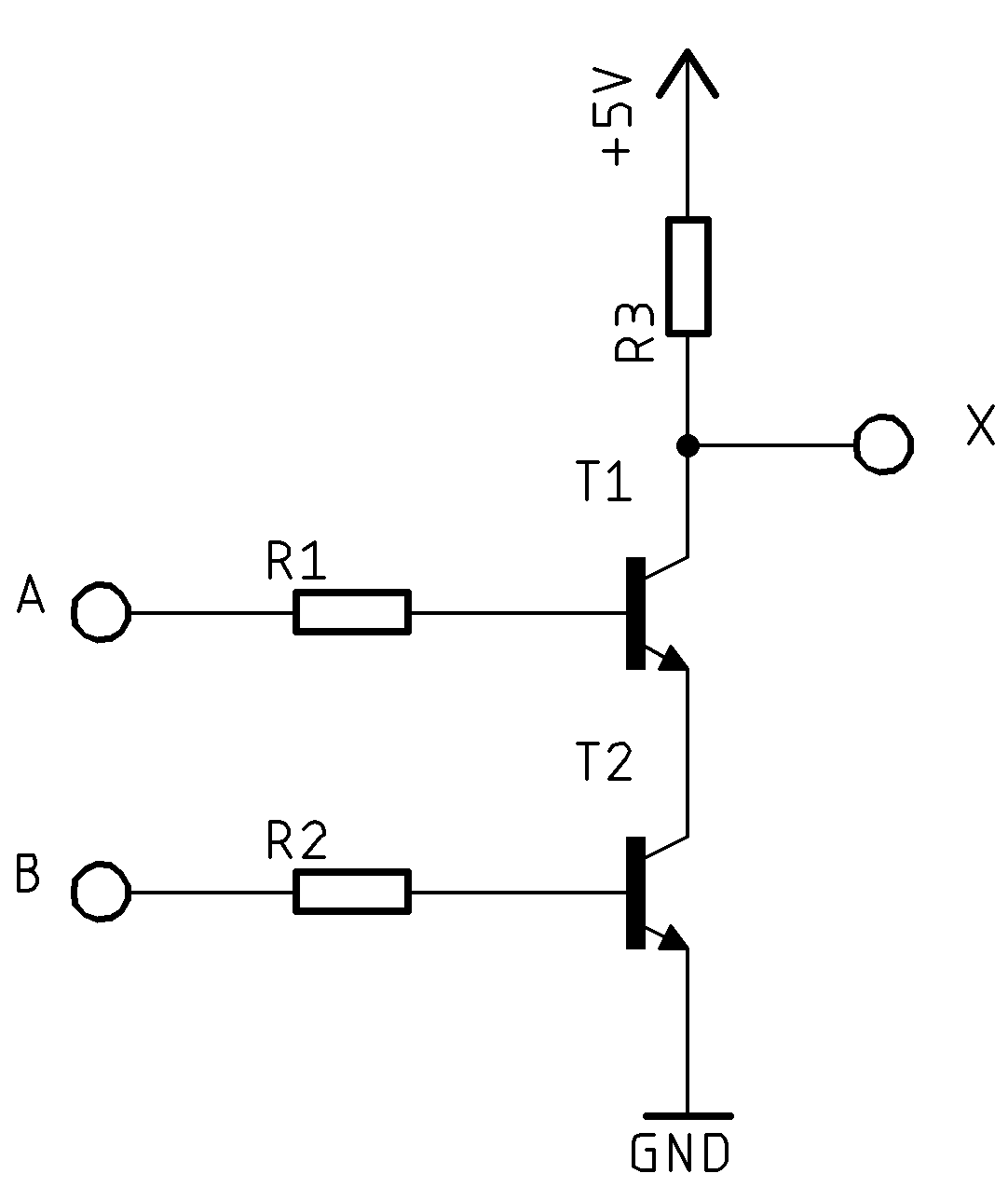

RTL-Schaltung

Am Beispiel eines NAND-Gatters:

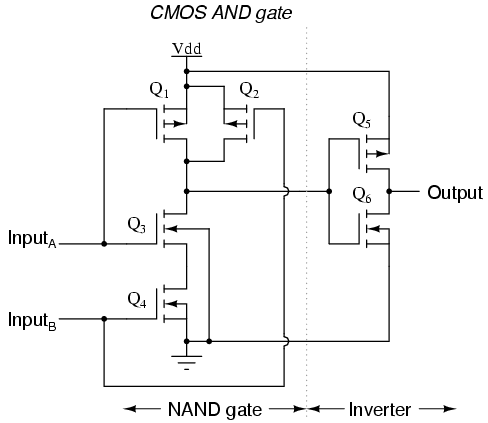

CMOS-Schaltung

- CMOS = complementary metal-oxide-semiconductor

- Integrierte Schaltungen, die sowohl p- als auch n-Kanal-MOSFETs verwenden.

Integrierte Schaltkreise

Aufgabe

An vier Digitalschaltungen werden jeweils die Eingangssignale \(A\) und \(B\) angeschlossen. Die Ausgangssignale der Digitalschaltungen sind im Bild mit \(X_1\) bis \(X_4\) angegeben. Zeichnen Sie den Aufbau der vier Digitalschaltungen.

Aufgabe

Die folgenden Eingangssignale \(A\) und \(B\) werden an die folgenden Schaltung angelegt. Zeichnen Sie das resultierenden Ausgangssignal \(X\).

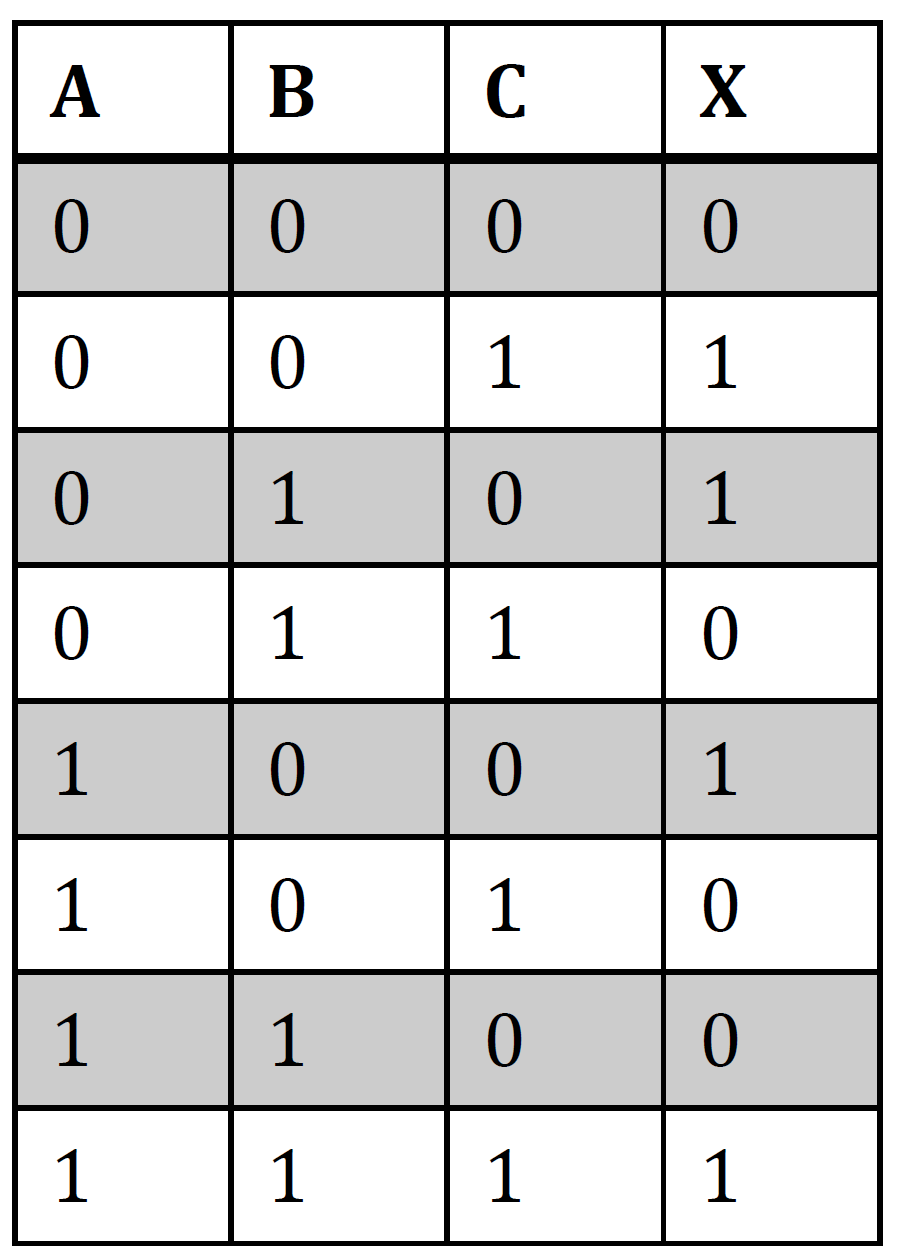

Aufgabe

Erstellen Sie den Schaltplan der Digitalschaltung, die die folgenden Wahrheitstabelle erfüllt.

Flip-Flops

RS-Flip-Flop

- Ein RS-Flip-Flop kann mit zwei NAND-Gattern aufgebaut werden

1 Unbekannter Zustand

2 Setzen

3 Halten

4 Löschen

5 Halten

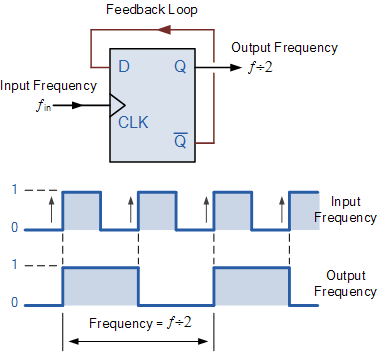

D-Flip-Flop

- Ein D-Flip-Flop besitzt einen Dateneingang (D) und einen Takteingang (T).

- Der Zustand des Dateneingangs wird für einen Taktzyklus gespeichert und am Ausgang ausgegeben.

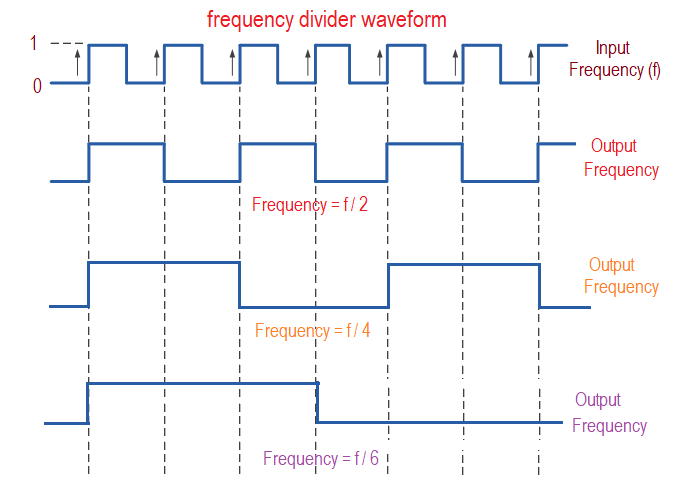

Frequenzteiler mit D-Flip-Flop

Rechentechnik

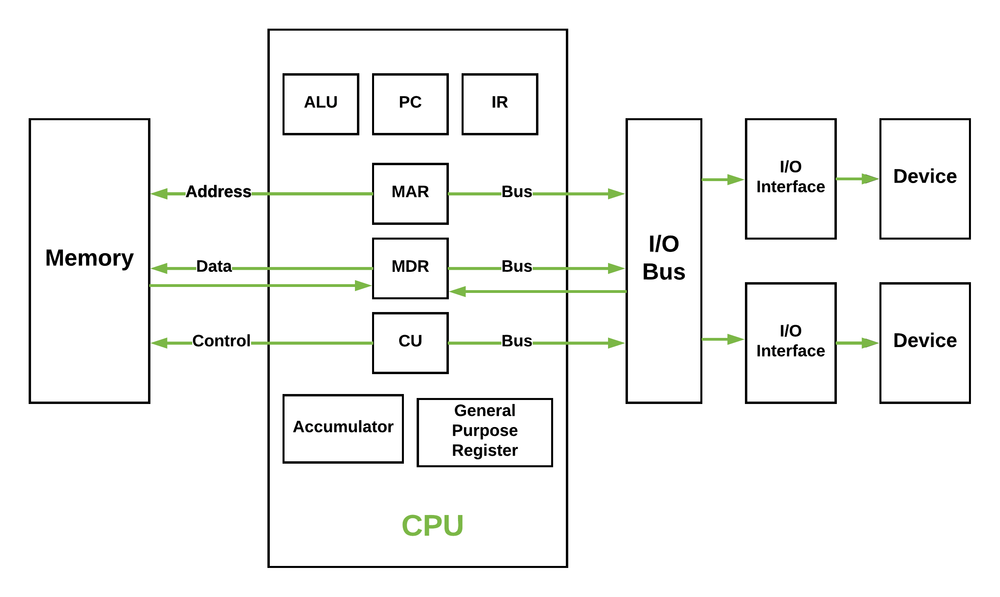

Aufbau einer CPU

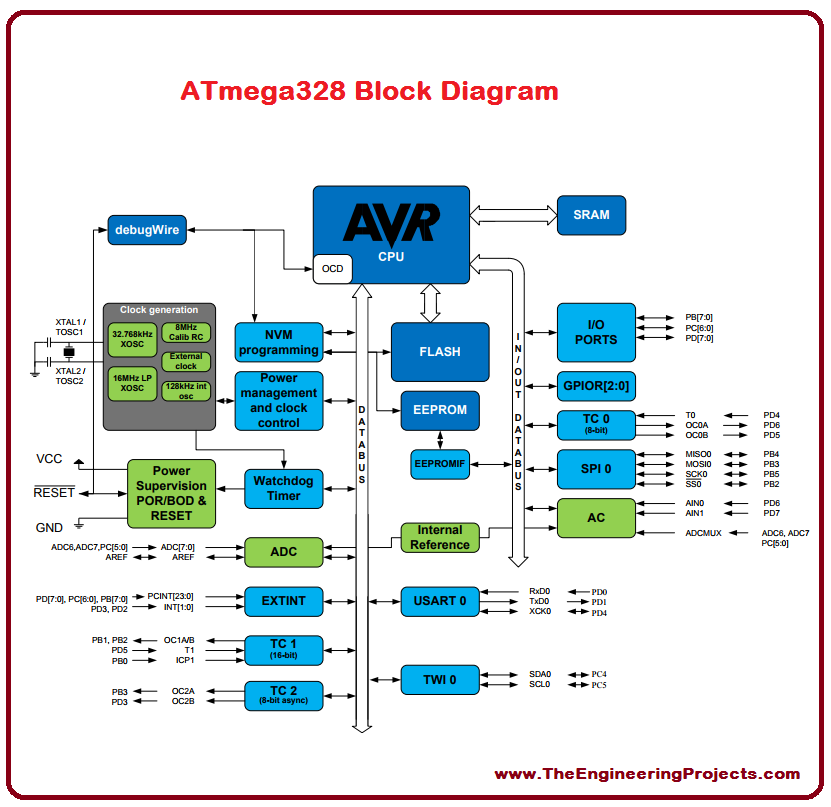

Aufbau eines Mikrocontrollers

Digitale Signalverarbeitung

Signalflussplan

Abtastfrequenz

- Das Nyquist-Shannon-Abtasttheorem beschreibt den Effekt, dass in der Folge \(x[n]\) nur dann die vollständige Information des analogen Signalverlaufs enthalten sein kann, wenn dessen höchsten Frequenzanteile \(f_{S,max}\) kleiner als die halbe Abtastfrequenz \(f_A\) sind.

- Wird das Abtasttheorem nicht eingehalten, so entstehen Aliasing-Effekte.